このページでは,Xilinx社のCPLDであるXC95ファミリの開発手順を解説しています.使用ツールは同社が無償で提供しているWebPACK ISE 6.2iです.

開発フローは大まかに次のようになります.

まず,プロジェクト・ナビゲータを起動します.Project Navigatorのショートカットがあれば,それをダブル・クリックします.あるいは,

スタート → すべてのプログラム → Xilinx ISE 6 → Project Navigator

とたどって,Project Navigatorを起動します.

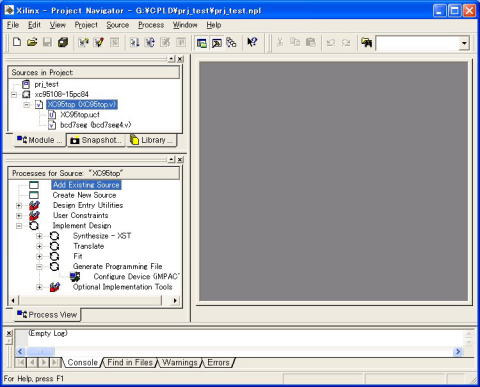

起動直後のウィンドウの様子を図1に示します.起動状況によって,若干異なることがあります.

図 1 Project Navigator起動時の様子

ウィンドウは大きく次の4つのサブ・ウィンドウにわかれています.

起動時に以前に実行していたプロジェクトがオープンされてる場合もあります(ツールの起動時にどのような状態にするかはメニュー・バーの Edit → Preferences... で設定できます).

【プロジェクトの設定】

最初に作業を行う場合は,プロジェクトを作成する必要があります.プロジェクトの作成は,メニュー・バーから次の

File → NewProject...

を選択します.すると次のウィンドウが現れます.

図2 新規プロジェクト作成

ここで,プロジェクトのフォルダを指定します.

Verilog-HDLのソース・ファイルがすでにある場合は,そのフォルダをプロジェクト用にするとよいでしょう.その場合,Project

Location欄にはソース・ファイルのあるひとつ上のフォルダを指定し, Project

Name欄には該当フォルダ名を指定します.

Verilog-HDLのソース・ファイルをこれから作成する場合は,Project Location欄には適当なフォルダを指定し,Project

Name欄にも適当なプロジェクト名を指定します.これにより,Project Location欄のフォルダの下にProject

Name欄で指定したプロジェクト名と同じフォルダが作成され,そのフォルダ下に各種ファイルが作られます.

【不 具 合 注 意】

現在,Verilog-HDLのファイルのあるフォルダとは別にプロジェクト・フォルダを作成すると,エディタで開かれるファイルと論理合成ツールが読み込むファイルが異なり,修正が反映されない不具合があります.

この不具合はVerilog-HDLのファイルのあるフォルダがプロジェクト・フォルダになるように設定を行うことで回避できます.

次のTop-level Module Typeの欄は HDL とします.もし,最上位レベルが回路図であれば Schematic を選択します.

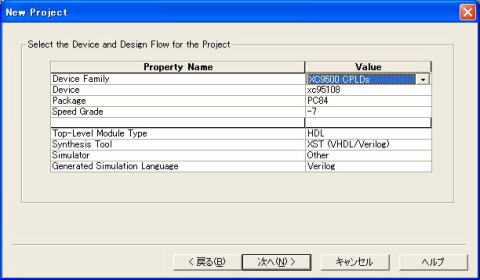

以上の設定の後,ボタン [ 次へ ] をクリックします.すると,次のデバイスの指定とデザイン・フローを指定するウィンドウが現れます.

図3 デバイスの指定とデザイン・フローの指定

まず,ここでは,使用するデバイスのファミリ,型番,パッケージ,スピード・グレードの指定を行います.

情報工学特論Ⅱでは,次の指定を行います.

次に,デザイン・フローの指定を行います.ここでは,論理合成ツールやシミュレータの指定,,生成されるシミュレーション言語(ハードウェア記述言語)の選択を行います.

情報工学特論Ⅱでは,次の指定を行います(重要なのはXSTの指定のみ).

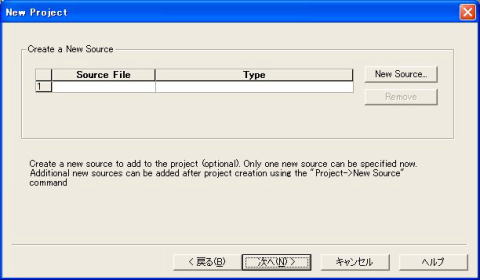

以上の設定の後,ボタン [ 次へ ] をクリックします.すると,次の新規HDLソース・ファイルの作成ウィンドウが現れます.

図 4 新規HDLソース・ファイルの作成

ここで,もし,新規にHDLソース・ファイルを作成する場合は,右上のボタン [ New Source...] をクリックし,ファイルの作成を行います.

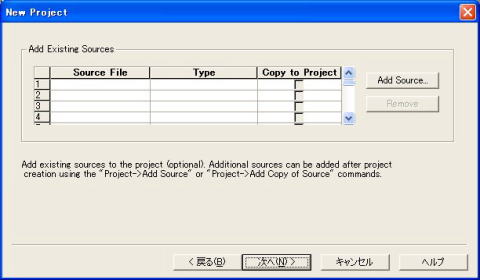

この段階ですでにHDLファイルを作成してある場合は,ここの設定はスキップし,ボタン [ 次へ ] をクリックします.すると,既存HDLソース・ファイルのプロジェクトへの追加ウィンドウが現れます.

図5 既存HDLソース・ファイルのプロジェクトへの追加

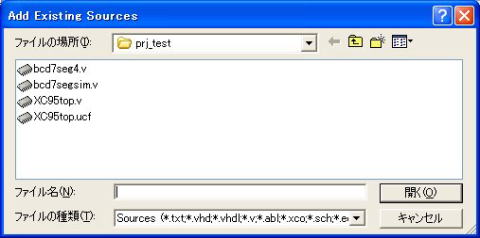

ここで,HDLファイルがすでにあれば,右上のボタン [ADD Source...] をクリックして次のウィンドウを表示し,HDLファイルを指定します.

図6 HDLソース・ファイル指定

ここで,に必要なVerilog-HDLファイルを指定します.シミュレーション用テスト・ベンチは指定対象外になります.また,端子信号と端子番号の対応を示す制約ファイル(拡張子は.ucf)がある場合は,これも合わせて指定します.

複数のファイルを指定する場合は, ctrl キーを押しながら必要なファイルを左クリックします.

情報工学特論Ⅱでは,制約ファイルとして, XC95top.ucf ファイルを指定します.これを指定しないと,後で全端子についてのピン番号指定を行うことになり,大幅に作業量が増加しミスの元にもなります.

以上,プロジェクトに登録するファイルの選択ができたら,ボタン [ 開く ] をクリックします.

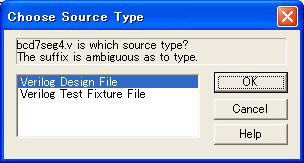

次に,登録するファイルに関するタイプを問い合わせてくるダイアログ・ウィンドウが現れるので,Verilog-HDLの設計対象ファイルかテスト・ベンチ(テスト・フィクスチャ)ファイルの指定をします(テスト・ベンチは通常指定しません).

図7 ファイルのタイプの問い合わせ

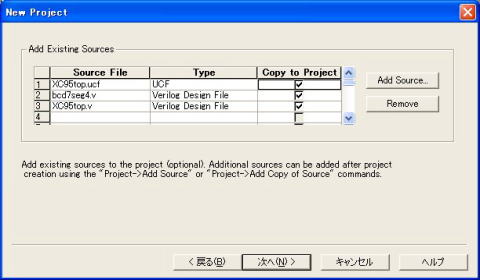

ファイルのタイプの指定が終了すると,指定したファイル名が図5のウィンドウに登録されます.

図8 プロジェクトへの登録ファイルの確認

もし,Verilog-HDLファイルが別のフォルダにある場合は, Copy to Project

欄にチェック印を付けると,プロジェクト・フォルダにファイルが登録されます.すでにプロジェクト・フォルダにVerilog-HDLファイルがある場合にはチェック印があってもなくても同じになります.

ファイルの確認後,ボタン [ 次へ ] をクリックしてプロジェクト作成を終了します.

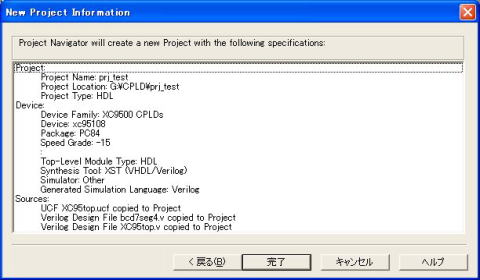

図9 プロジェクト情報の確認ウィンドウ

ここで,プロジェクト情報が表示されますので,確認後,ボタン [ 完了 ]をクリックします.

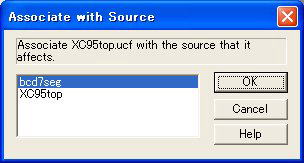

図10 制約ファイルの対象モジュールの指定

さらに,制約ファイルをプロジェクトに登録した場合は,その制約がどのモジュールに対するものであるかを指定します.

情報工学特論Ⅱの場合,制約ファイルは端子番号の指定になりますので,最上位記述 XC95top になります.

ここで,左上のモジュールの階層構造ウィンドウ上で最上位のジュールを指定(左クリックしてハイ・ライト)します.

階層構造ウィンドウ上で,下位のモジュールや別のファイルを指定すると,下位の階層のみの論理合成・配置配線作業だけが行われたり,論理合成・配置配線作業ができないことになりますので,注意して下さい.

図11 プロジェクト設定終了後のウィンドウ

情報工学特論Ⅱの場合は XC95top (XC95top.v) を指定します.

また,左中にある各種処理の起動とステータス・ウィンドウでは,Implement Design 以下が展開されていない場合(左端にあるボタンが [ + ] になっている場合)は,左端のボタン [ + ] をクリックして展開しておきます.

展開すると,論理合成・配置配線からデバイス・プログラミングを行うための一連の作業コマンドが表示されます.

論理合成・配置配線からデバイス・プログラミングまでの作業は,Implement

Design 以下にある項目の上から順番に実行(ダブル・クリック)していきます.なお,最下段にあるOptional

Implementation Toolsは使用しません.

各処理コマンドの左側には以下の印が付き(最初は空欄),処理の状況を把握することができます.

また,各処理を開始すると,下にあるメッセージ・ウィンドウに各種の情報が表示されます.処理終了後,スクロールして確認します.

これはあとで,各処理の左側にあるボタン [ + ]をクリックして展開し,レポート・ファイルをダブル・クリックすることでも参照できます.

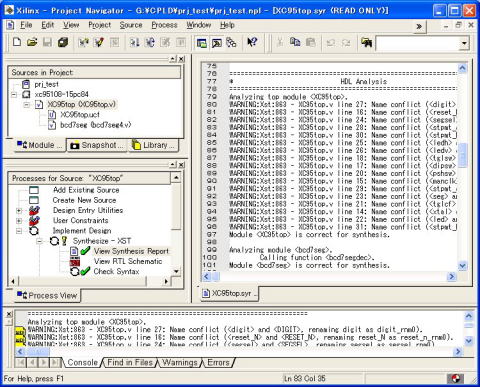

図12 論理合成後のレポート・ファイルの参照の様子

まず,最初にSynthesize(論理合成)をダブル・クリックして実行します.

情報工学特論Ⅱでは次のようなワーニング・メッセージがでます.

=========================================================================

* HDL Analysis *

=========================================================================

Analyzing top module <XC95top>.

WARNING:Xst:863 - XC95top.v line 27: Name conflict (<digit> and <DIGIT>,

renaming digit as digit_rnm0).

WARNING:Xst:863 - XC95top.v line 16: Name conflict (<reset_N> and <RESET_N>, renaming reset_N as reset_n_rnm0).

WARNING:Xst:863 - XC95top.v line 24: Name conflict (<segsel> and

<SEGSEL>, renaming segsel as segsel_rnm0).

途中省略

=========================================================================

* HDL Synthesis * ========================================================================= Synthesizing Unit <bcd7seg>.

Related source file is bcd7seg4.v.

Found 16x7-bit ROM for signal <$old_bcd7segdec/1/out_2>.

Summary: inferred 1 ROM(s).

Unit <bcd7seg> synthesized.

Synthesizing Unit <XC95top>.

Related source file is XC95top.v.

WARNING:Xst:646 - Signal <manclk_rnm0> is assigned but never used.

WARNING:Xst:653 - Signal <ledh_rnm0> is used but never assigned.

Tied to value 00000000.

WARNING:Xst:653 - Signal <stpmt_b_rnm0> is used but never assigned.

Tied to value 0.

前者は「同じスペルで大文字の信号と小文字の信号がある」ことを示すものです.本来のVerilog-HDLでは大文字と小文字は別もとのして区別されますが,Xilinx社のツールでは,この区別がなされないため,リネームした旨の注意が表示されます.このワーニングは外部端子に関するのもに限って無視して問題ありません.

後者のメッセージは未接続信号に関するもので,2種類あります.1つ目は信号の接続先がないもので,2つ目は値の代入されていない信号が使われている場合です.

つまり,入力端子として定義されているのに,内部で使用していないものがある場合は,

Signal <信号名> is assigned but never used

出力端子として定義されているが内部で接続がない場合は,

Signal <信号名> is used but never assigned. Tied to value 0.

というメッセージが出ます.この2つのワーニング・メッセージは問題がないことを確認する必要があります.

情報工学特論ⅡではCPLD実習ボード上でスイッチやLEDが接続されていますので,使わない機能につながる信号かどうか確認する必要があります.使用する信号に対してこれらのワーニングが出ている場合は修正が必要です.

これ以外のワーニング・メッセージが出た場合は,よく読んで修正が必要な場合には適切な処置を行います.

次に, Translate (ネット・リストや制約ファイルの統合)を実行します.

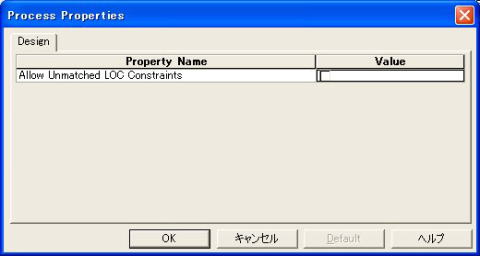

情報工学特論Ⅱでは,まず最初に Translate を右クリックしてProperties を選択して,次のウィンドウを表示します.

図13 Translateのプロパティ設定

ここで, Allow Unmatched LOC Constraints Value にチェック印を付け,ボタン [ OK ] をクリックします.これは,未使用端子と制約ファイルでの端子番号指定の不一致によるエラーを出さないようにするために必要になります.

この設定は必要に応じて行って下さい(端子番号制約をISE上で行う場合などは).以上の設定後, Translate をダブル・クリックして実行します.通常,この処理ではエラーやワーニングは出ません.

次に, Fit (ネット・リストをCPLDの内部構造にフィット.... つまり配置配線)作業を行います.これは Fit をダブル・クリックするだけで,他の設定は必要ありません.

情報工学特論ⅡではFitを実行すると,次のようなワーニング・メッセージがでます.

Started process "Fit".

Release 6.2.02i - CPLD Optimizer/Partitioner G.30 Copyright (c) 1995-2004 Xilinx, Inc. All rights reserved.

WARNING:Cpld:1007 - Removing unused input(s) 'DIPSW<0>'. The input(s)

are

unused after optimization. Please verify functionality via simulation.

WARNING:Cpld:1007 - Removing unused input(s) 'DIPSW<1>'. The input(s)

are

unused after optimization. Please verify functionality via simulation.

これは使用していない端子に対するもので,最適化後,使用されていない信号を削除した旨のメッセージです.使用しない端子についてこのワーニングが出ている場合は無視できます.が,使用している信号に対して出た場合にはチェックが必要です.

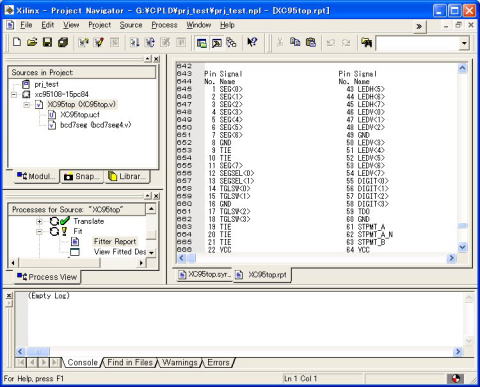

情報工学特論ⅡではFitter Report を開いて端子信号と端子番号の確認を必ず行って下さい.万が一,制約ファイルの指定を誤っていると,端子信号と端子番号の不一致が発生し,正しく動作しないだけでなく,CPLDの破壊の原因になります.

Fitter ReportはFit の左側にあるボタン [ + ] をクリックして展開し,Fitter

Report をダブル・クリックします.

図14 Fitter Reportによる端子信号と端子番号の確認

端子情報はファイルの後の方にあります.スクロールして確認します.なお,端子信号名と端子番号の対応は XC95top.ucf ファイル(プリント配布済み)に記載してあります.

〔プログラミング・ファイルの生成 ジェネレイト・プログラミング・ファイル〕

Fit 作業後,ワーニング・メッセージの確認と,端子番号の確認を行ったら, Generate Programming FIle を実行します.これはCPLDへ書き込む回路情報のファイルの生成を行います.通常,ここではエラーやワーニングは出ません.

以上の作業が終了した段階で,プロジェクト・フォルダにJEDECフォーマットのファイル(拡張子.jed)が生成されています.このファイルがCPLDへ書き込む情報になります.

一般には次にCPLDへの書き込み作業を行います.書き込み作業はGenerate Programming

FIle の下にある Configure Device (iMPACT)をダブル・クリックして,CPLDへの書込みプログラムを起動します.

だたし,情報工学特論Ⅱでは,ここでCPLD実習装置のあるパソコンに移動して続きの作業を行うことになります.

情報工学特論Ⅱの場合,ここまで進んだ段階で生成された XC95top.jed という名前のファイル(プロジェクト・フォルダにあります)をフロッピー・ディクス等へコピーしてCPLD実習ボードのあるパソコンへ移動し,次の手順でプログラム(iMPACT)を起動します.

DOSプロンプトを起動する.

DOSプロンプトにおいてファイルのあるディレクトリまで移動する

ドライブの移動は ドライブレター:

ディレクトリの移動は cd ディレクトリ名

コマンド入力で iMPACT を起動する.

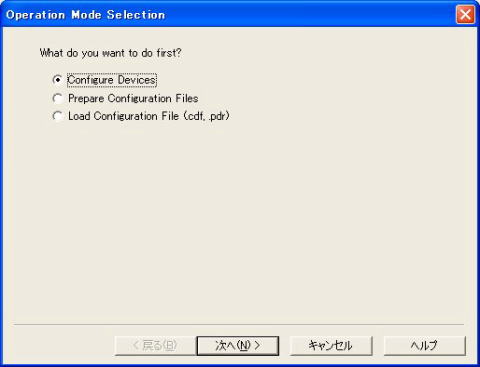

次のウィンドウが現れますので, Configure Device を選択してボタン [ 次へ

] をクリックします.

図15 iMPACT起動後の機能選択

以降は次の作業と同じになります.

ここまで作業が進んだところで,ようやくデバイス(CPLD)のプログラミング(機能設定作業)を行える状態になります.

まず, Generate Programming FIle の下にある Configure Device (iMPACT)をダブル・クリックして,CPLDへの書込みプログラムを起動します.

すると,基本ウィンドウの他に次にサブ・ウィンドウが開きます.

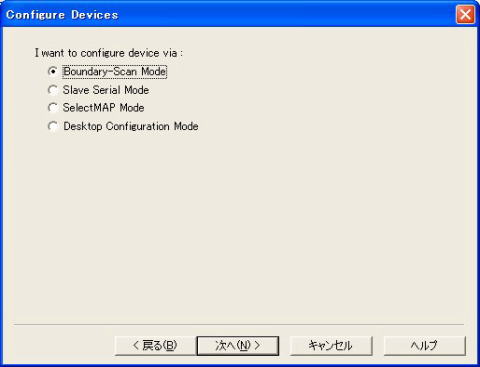

図16 CPLDのプログラミング(コンフィギュレーション)方法の指定

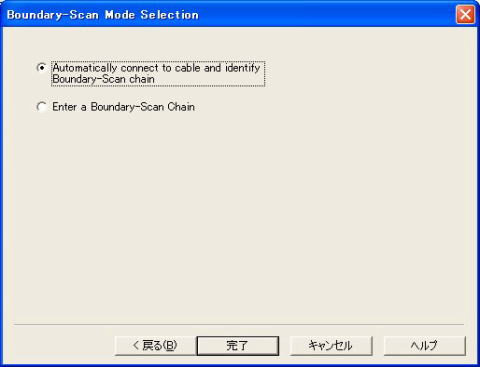

ここでは,最上部にある Boundary-Scan Mode を選択肢,ボタン [ 次へ ] をクリックします.すると次にバウンダリ・スキャン・モードの選択ウィンドウが現れますので,そのまま(Automatically .... を選択)ボタン [ 完了 ] をクリックします.

図17 バウンダリ・スキャン・モードの選択ウィンドウ

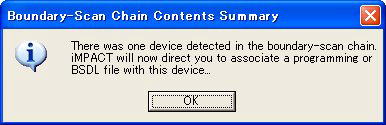

その後,いくつかの状況表示ウィンドウが現れて消えますが,最後に次のウィンドウが現れます.ここは単にボタン [ OK ] をクリックします.

図18 デバイスの確認ウィンドウ

次に,どのファイルを使ってCPLDをプログラム(コンフィギュレーション)するか,ファイルを指定ウィンドウが表示されます.

図19 コンフィギュレーション・ファイルの指定

ここで,ファイル(拡張子は.jed)を指定しボタン [ 開く ] をクリックします.

情報工学特論Ⅱでは, コンフィギュレーション・ファイルは全て XC95top.jed となります.特にファイルのあるフォルダに注意してください.

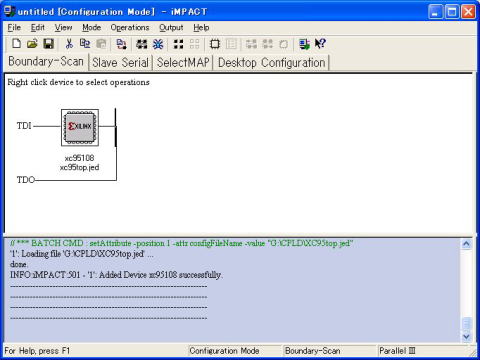

図20 バウンダリ・スキャン・チェイン上のデバイスとコンフィギュレーション・ファイルの様子

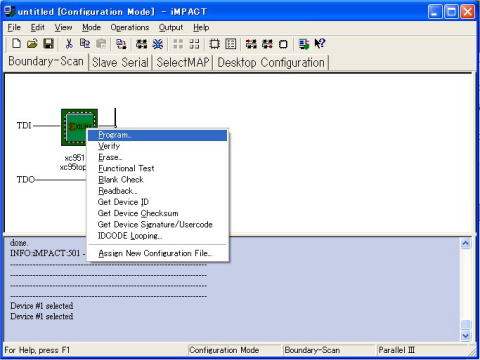

ここで,デバイスのアイコンを右クリックして,メニューを出し, Programmingを選択します.

図21 デバイスのプログラミングの開始

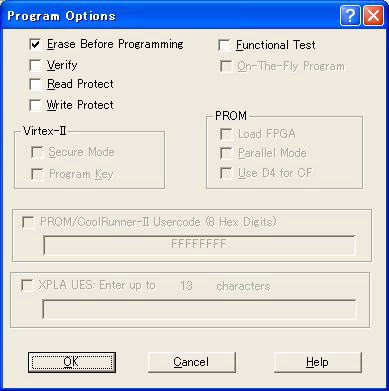

ここで,プログラミング・オプション・ウィンドウが表示されますので, Erase Before Programming を選択(デフォルトでそうのようになっている)し,ボタン [ OK ] をクリックします.

図22 プログラミング・オプションの指定

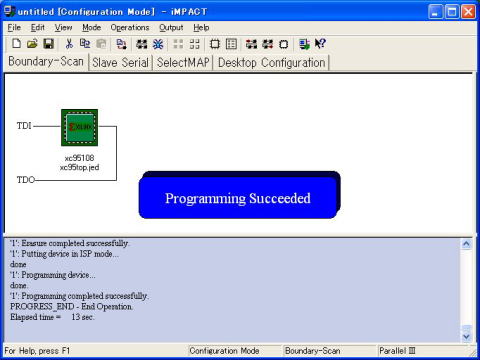

これで,まずCPLDに設定されているコンフィギュレーション・データの消去が行われます(少々,時間がかかります).次いで,指定した

.jed ファイルの情報がCPLDへ書き込まれます.

進行状況が表示され,正常終了すると,次のウィンドウが現れます.

図23 デバイス・コンフィギュレーションの正常終了

この段階で,CPLDは機能を開始しています.