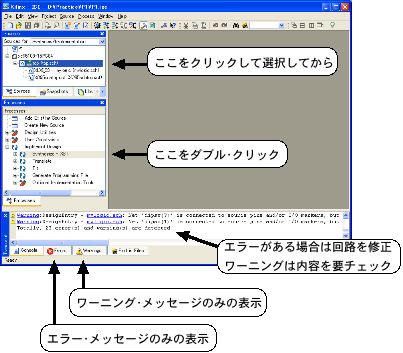

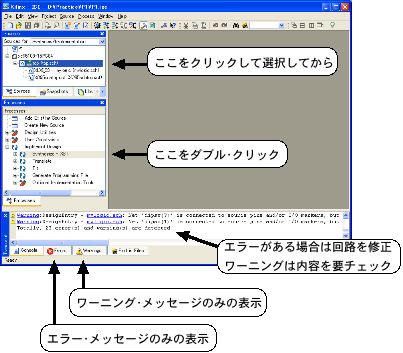

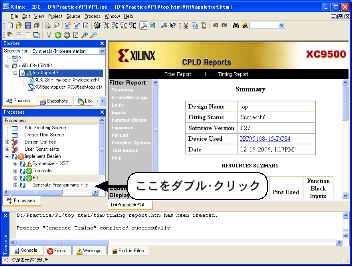

<図12 論理合成>

[5] 配置配線〜CPLDデバイス・プログラミング・ファイルの生成

回路図の入力が完了したら,CPLDへ設定する回路情報ファイル(デバイス・プログラミング・ファイル ... コンフィギュレーション・ファイルともいう)を生成する.

主な作業を次に示す(Implement Designのサブ・メニューにある).

€Synthesize ... 論理合成(実際には合成作業はなく,回路情報の変換作業)

Translate ... 回路接続情報や端子制約情報を統合

¡Fit ... 各パーツをCPLD上のリソースに対応させ配線するための情報を生成

¤Generate Programming File ... CPLDに設定する回路情報ファイルを生成

【注意】ソース・エリアで最上位モジュール(top)を選択してから以下の作業を行うこと.

€Synthesize

まず,処理対象の最上位モジュールを指定する.ソース・エリアにある"top"モジュールをクリックして回路全体に対して作業するよう設定する.回路図エディタ終了時点では修正したモジュールが選択されているので,注意すること.

<図12 論理合成>

次いで,プロセス・エリアで "Synthesize" をダブル・クリックして論理合成をおこなう.

論理合成を開始すると,進行度合がウィンドウの右下に表示され,メッセージ・エリアに各種メッセージが表示される.エラーがあると赤いアイコンのメッセージが,ワーニングは黄いアイコンがついたメッセージが表示される.メッセージ・エリアの下についているタブでエラーのみ/ワーニングのみを表示することもできる.

エラーは必ず修正が必要になるので,メッセージを問題箇所の発見のヒントとする.

ワーニングには無視してよいものと,修正が必要なものがある.無視してよいワーニングは「未接続の入力端子」に関するもので,それ以外は何らかの問題があるので修正する.

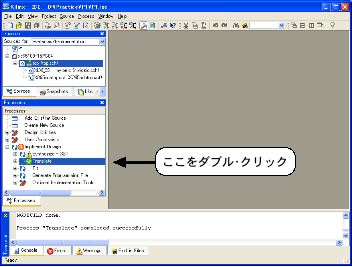

translate

次に各種入力ファイルの統合作業をおこなう.プロセス・エリアの"Translate"をダブル・クリックする.

<図13 translate処理>

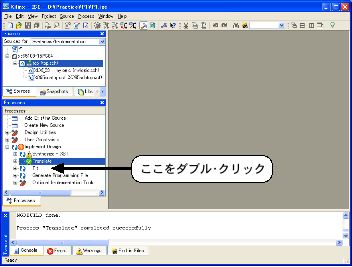

¡Fit

設計情報を元に,デバイス上に部品を配置し配線するための情報を生成する作業として"Fit"をダブル・クリックする. TranslateやFitの途中でエラーやワーニングが発生したらよく確認すること.

エラーの場合は必ず修正する必要がある.ワーニングは内容によっては無視してもよいこともある(意味を理解せずに無視しないこと).

<図14 Fit処理>

¤Generate Programming File

"Generate Programming File"をダブル・クリックして起動する.

<図15 Generate Programming Files処理>